# 第7章 并行扩展技术

(课时: 4学时)

## 教学目的

- 了解数据总线、地址总线和控制总线的构成。

- 掌握片外扩展程序存储器和数据存储器的方法。

- · 掌握扩展I/0的方法和可编程芯片8255及8155的应用。

# 学习重点和难点

- 控制总线的构成方法和扩展存储单元地址的分析方法。

- 8255A与8155的应用。

# 第7章 并行扩展技术

- 7.1 并行扩展概述

- 7.2 程序存储器扩展

- 7.3 数据存储器扩展

- 7.4 简单并行I/0接口扩展

- 7.5 8255可编程并行接口扩展

- 7.6 8155可编程并行接口扩展

- 本章小结

- 习题

# 7.1 并行扩展概述

- 7.1.1 总线

- 7.1.2 扩展总线的实现

- 总线是单片机应用系统中,各部件之间传输信息的 通路,为CPU和其他部件之间提供数据、地址以 及控制信息。

- 按总线所在位置可分:内部总线和外部总线,前者 是指CPU系统内部各部件之间的通路,后者指 CPU系统和其外围单元之间的通路,通常所说总 线是指外部总线。

- · 按通路上传输的信息可分:数据总线(DB, Data Bus)、地址总线(AB, Address Bus)和控制总线 (CB, Control Bus)。

### 1. 数据总线

- 数据总线(DB)用于单片机与存储器之间或单片机与I/O端口 之间传输数据。

- 数据总线的位数与单片机处理数据的字长一致,如8051单 片机是8位字长,数据总线的位数也是8位。

- 从结构上来说数据总线是双向的,即数据既可以从单片机 送到I/O端口,也可以从I/O端口送到单片机。

### 2. 地址总线

- 地址总线AB用于传送单片机送出的地址信号,以便进行存储单元和I/O端口的选择。

- 地址总线的位数决定了单片机可扩展存储容量的大小。如 8051单片机地址总线为16位,其最大可扩展存储容量为 216=64K字节。

- · 地址总线是单向的,因地址信息总是由CPU发出的。

### 3. 控制总线

控制总线用来传输控制信号,其中包括CPU送往外围单元的控制信号,如读信号、写信号和中断响应信号等;还包括外围单元发给送给CPU的信号,如时钟信号、中断请求信号以及准备就绪信号等。

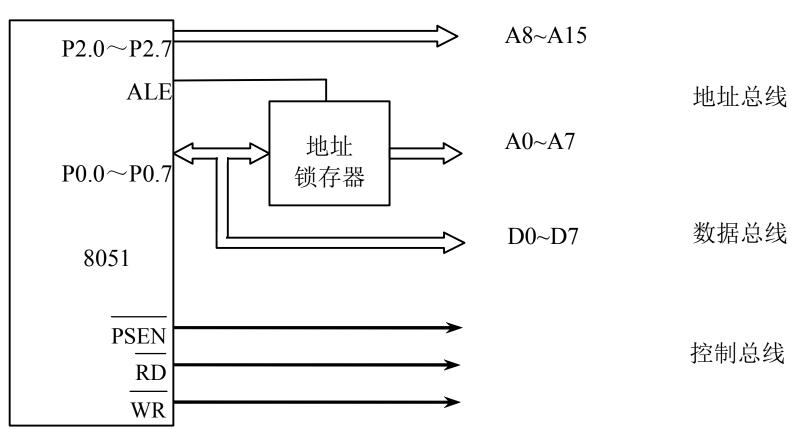

#### 单片机的三总线结构

### 1. 并行扩展总线组成

80C51系列总线型单片机中,由PO口做地址/数据复用口; P2口做地址线的高八位; P3口的RD、WR加上控制线EA、 ALE、PSEN等组成控制总线。

#### (1) 地址总线A0~A15

- 地址总线的高8位是由P2口提供的,低8位是由P0口提供的。

- 在访问外部存储器时,由地址锁存信号ALE的下降沿把P0口的低8位以及P2口的高8位锁存至地址锁存器中,从而构成系统的16位地址总线。

- 实际应用系统中,高位地址线并不固定为8位,需要用几位就从P2口中引出几条口线。

### (2) 数据总线D0~D7

- 数据总线是由P0口提供的,因为P0口线既用作地址线,又用作数据线(分时使用),因此,需要加一个8位锁存器。

- 在实际应用时,先把低8位地址送锁存器暂存,然后再由地址锁存器给系统提供低8位地址,而把P0口线作为数据线使用。

- · 在读信号RD与写信号WR有效时,P0口上出现的为数据信息。

### (3) 控制总线

系统控制总线共12根,既P3口的第二功能再加上RESET、EA、ALE和PSEN。实际应用中的常用控制信号如下。

- 使用ALE作为地址锁存的选通信号,以实现低8位地址的 锁存。

- 以PSEN信号作为扩展程序存储器的读选通信号。

- 以EA信号作为内、外程序存储器的选择信号。

- 以RD和WR作为扩展数据存储器和I/O端口的读、写选通信号。执行MOVX指令时,这两个信号分别自动有效。

#### 2. 总线扩展的特性

### (1) 三态输出

总线在无数据传送时呈高阻态,可同时扩展多个并行接口器件,因此存在寻址问题。单片机通过控制信号来选通芯片,然后实现一对一的通信。

### (2) 时序交互

单片机并行扩展总线有严格的时序要求,该时序由单片机的时钟系统控制,严格按照CPU的时序进行数据传输。

### (3) 总线协议的CPU控制

通过并行总线接口的数据传输,不需要握手信号,双方都严格按照CPU的时序协议进行,也不需要指令的协调管理。

- 并行总线扩展的主要问题是总线连接电路设计、器件的选择以及器件内部的寻址等。

- 并行总线扩展时,其所有的外围扩展设备的并行总线引脚都连到相同的数据总线(DB)、地址总线(AB)以及公共的控制总线RD、WR上。其中数据总线为三态口,在不传送数据时为高阻态。总线分时对不同的外设进行数据传送。

- 总线连接方式的重点在于外围设备片选信号的产生。该信号主要由以下两种方法产生。

- 线选法:用所需的低位地址线进行片外存储单元I/O端口寻址,余下的高位地址线输出各芯片的片选信号,当芯片对应的片选地址线输出有效电平时,该芯片选通操作。

- 译码法:该方法需要用到译码器。采用译码法时,仍由低位地址线作片外寻址,而高位地址线用于译码器的输入,译码器的输出信号作各芯片的选通信号。

# 7.2 程序存储器扩展

- 7.2.1 常用程序存储器芯片

- 7.2.2 程序存储器扩展实例

## 7.2.1 常用程序存储器芯片

- 单片机外部扩展常用程序存储器芯片为EPROM,其掉电后信息不会丢失,且只有在紫外线的照射下,存储器的单元信息才可擦除。

- 用作扩展的EPROM主要是27系列,如2716、2732、2764、27128、27256等,其中高位数字27表示该芯片是EPROM,低位数字表明存储容量,如2716表示16K个存储位,亦即字节容量为2K的EPROM。

- 常用的还有EEPROM , 即28系列, 如2816/2817、2864

等,型号含义同上。

### 7.2.1 常用程序存储器芯片

- 常用EPROM芯片管脚和封装如下图所示。EPROM除2716 外均为28线双列直插式封装,各引脚定义如下。

- A0~Ai: 地址输入线,i=12~15。

- D0~Di: 三态数据总线,读或编程校验时为数据输出线, 编程时为数据输入线。其余时间呈高阻状态。

- · PGM:编程脉冲输入线。

- OE: 读出选通线,低电平有效。

- CE: 片选线,低电平有效。

- V<sub>PP</sub>:编程电源线,其值因芯片及制作厂商而异。

- V<sub>cc</sub>: 电源线,接+5V电源。

- GND:接地。

### 7.2.1 常用程序存储器芯片

- EPROM的操作方式主要有以下几种。

- · 编程方式:把程序代码(目标文件)固化到EPROM中。

- 编程校验方式:读出EPROM中的内容,校验编程操作的正确性。

- 读出方式: CPU从EPROM中读出代码。

- 维持方式:数据端呈高阻态。

- 编程禁止方式:用于多片EPROM并行编程。

#### 2764和27128的操作方式

| 引脚↩ 方式↩ | Œ ↔<br>(20) <i>↔</i>                                                | <br>CE +<br>(22) ₽                                 | PGM ↔<br>(27)↔            | V <sub>PP</sub> +/<br>(1) 4 | Vcc+<br>(28) ₽ | Q0~Q7≠<br>(11~13 15~19)≠ | ٩  |

|---------|---------------------------------------------------------------------|----------------------------------------------------|---------------------------|-----------------------------|----------------|--------------------------|----|

| 读₽      | $V_{\mathrm{IL}^{\wp}}$                                             | $V_{\mathrm{IL}^{4^{3}}}$                          | $V_{\mathrm{IH}^{arphi}}$ | $V_{CC^{4^{2}}}$            | 5V₽            | Dout₽                    | ته |

| 禁止输出₽   | $V_{\mathrm{IL}^{\wp}}$                                             | $V_{IH^{arphi}}$                                   | $V_{IH^{arphi}}$          | $V_{CC^{e^2}}$              | 5V <i>₽</i>    | 高阻↩                      | ته |

| 维 持₽    | $V_{\mathrm{IH}^{\scriptscriptstyle arphi^{\scriptscriptstyle 2}}}$ | Χø                                                 | X₽                        | $V_{CC^{e^{j}}}$            | 5V₽            | 高阻↵                      | 42 |

| 编 程4    | $V_{\mathrm{IL}^{\wp}}$                                             | $V_{\mathrm{IH}^{\scriptscriptstyle 4^{\supset}}}$ | V <sub>IL</sub>           | **                          | * **           | Din₽                     | ٠  |

| 编程校验₽   | $V_{\mathrm{IL}^{\wp}}$                                             | $V_{\mathrm{IL}^{\wp}}$                            | $V_{IH^{\wp}}$            | **                          | * **           | Dout∂                    | 43 |

| 编程禁止₽   | $V_{\mathrm{IH}^{\scriptscriptstyle \circ}}$                        | Χø                                                 | Χø                        | **                          | * **           | 高阻₽                      | 47 |

#### 27256的操作方式

| 引脚      | \$4.0000.00                           | ŌE ₽                      | V <sub>PP</sub> * | Vcc≁  | Q0~Q7₽         |  |

|---------|---------------------------------------|---------------------------|-------------------|-------|----------------|--|

| 方式↩     | (20)                                  | (22)₽                     | (1)₽              | (28)₽ | (11∼13 15∼19)₽ |  |

| 读₽      | $V_{\mathrm{IL}^{e^2}}$               | $V_{\mathrm{IL}^{\wp}}$   | $V_{CC^{e^2}}$    | 5V₽   | Dout∉          |  |

| 禁止输出。   | $V_{\mathrm{IL}^{\epsilon^{\jmath}}}$ | $V_{\mathrm{IH}^{arphi}}$ | $V_{CC^{arphi}}$  | 5V₽   | 高阻₽            |  |

| 维持型     | $V_{\mathrm{IH}^{4^3}}$               | Χø                        | $V_{CC^{arphi}}$  | 5V₽   | 高阻₽            |  |

| 编 程₽    | $V_{\mathrm{IL}^{arphi}}$             | $V_{\mathrm{IH}^{\wp}}$   | ***               | * *** | Din₽           |  |

| 编程校验♪   | $V_{\mathrm{IL}^{\wp}}$               | $V_{IL^{\wp}}$            | *43               | * **  | Dout∂          |  |

| 编程禁止₽   | $V_{\mathrm{IH}^{4^3}}$               | $X_{\phi}$                | ***               | * *4  | 高阻₽            |  |

| 选择编程校验4 | $V_{\Pi^{e^{\mathfrak{I}}}}$          | $V_{\Pi^{e^j}}$           | $V_{CC^{arphi}}$  | * **  | Dout           |  |

#### 27512 的操作方式

| 引脚↵             | Œ ₽<br>(20)₽              | 0E /V <sub>PP</sub> +/ (22) ₽ | V <sub>cc</sub> .<br>(28) ₽ | Q0~Q7≠<br>(11~13 15~19)≠ |  |

|-----------------|---------------------------|-------------------------------|-----------------------------|--------------------------|--|

| ·<br>读 <i>a</i> | V <sub>IL</sub>           | $V_{\mathrm{IL}^{\wp}}$       | 5V₽                         | Dout₽                    |  |

| 禁止输出↩           | $V_{\mathrm{IL}^{\wp}}$   | $V_{\mathrm{IH}^{arphi}}$     | $V_{CC^{arphi}}$            | 高阻₽                      |  |

| 维持₽             | $V_{\mathrm{IH}^{4^{3}}}$ | $X_{\ell}$                    | $V_{CC^{arphi}}$            | 高阻₽                      |  |

| 编程₽             | $V_{\mathrm{IL}^{arphi}}$ | $12.5 V \pm 0.5 V_{\phi}$     | 6V₽                         | Din₽                     |  |

| 编程校验₽           | $ m V_{IL^{\wp}}$         | V <sub>IL</sub> 4             | 6V.₽                        | Dout₽                    |  |

| 编程禁止₽           | $V_{\mathrm{IH}^{4^{j}}}$ | 12.5V ± 0.5V₽                 | 6V₽                         | 高阻↩                      |  |

注: X 代表任意状态。

\* 代表VPP的大小与型号和编程方式有关。

\*\*代表VCC的大小与型号和编程方式有关。

## 7.2.2 程序存储器扩展实例

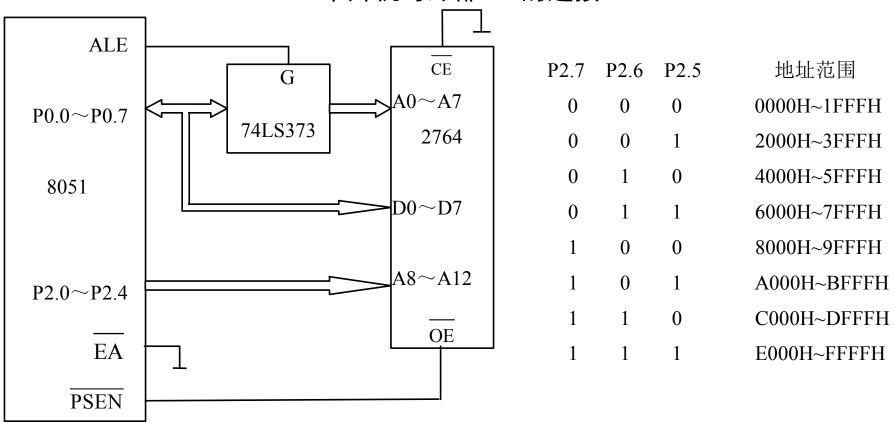

【例1】 8051扩展一片2764 EPROM(8KB)。

解: P2口的P2. 0~P2. 4与EPROM的高5位地址线及片选CE连接;P0口经地址锁存器输出的地址线与EPROM的低8位地址线相连,同时P0口又与EPROM的数据线相连;单片机ALE连接锁存器的锁存控制端;PSEN接EPROM的输出允许OE;8051的内、外存储器选择端EA接地。

扩展单片EPROM, 其片选CE直接接地即可。只要系统执行读外部程序存储器的指令,该EPROM就处于选通操作。P2口的P2.5~P2.7未用,所以它们的状态与2764的寻址无关;P2.5~P2.7有八种状态,2764的寻址范围对应有八个映像区。

### 7.2.2 程序存储器扩展实例

#### 单片机与外部ROM的连接

# 7.3 数据存储器扩展

- 7.3.1 常用数据存储器芯片

- 7.3.2 数据存储器扩展实例

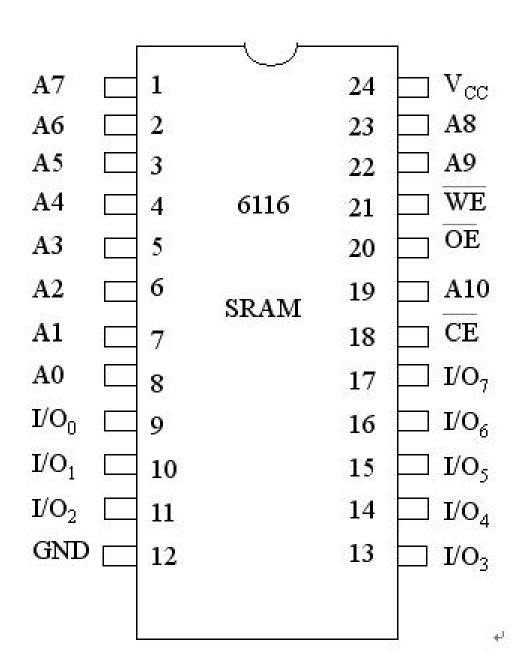

### 7.3.1 常用数据存储器芯片

- 数据存储器用于存储现场采集的原始数据、运算结果等。 外部数据存储器应能随机读/写,通常由半导体静态随机读/ 写存储器RAM组成。EEPROM芯片有时也会用作外部数据 存储器。

- · 静态RAM主要有读出、写入、维持三种工作方式。

- 常用的静态RAM(SRAM)电路有61系列的6116以及62系列的6264、62128、62256等。

### 7.3.1 常用数据存储器芯片

#### 各引脚定义如下:

- A0~Ai: 地址输入线, i=10(6116), 12(6264),

13(62128) 14(62256)。

- D0~Di:双向三态数据线(6116为I/O₀~I/O₁)。

- CE: 片选信号输入端,低电平有效。6264的26脚(CS1)为高电平,且CE为低电平时才选中该片。

- OE: 读选通信号输入端,低电平有效。

- WE:写允许信号输入端,低电平有效。

- V<sub>cc</sub>: 工作电源,接+5V电压。

- GND:接地。

#### 6116的引脚与封装

### 62系列SRAM引脚与封装

| 62256         | 62128 | 6264                   |        | 6                           | 264 62128           | 62256                 |

|---------------|-------|------------------------|--------|-----------------------------|---------------------|-----------------------|

| A14           | NC    | NC 1                   | $\cup$ | 28   V                      | $ m_{cc}$ $ m_{cc}$ | $\rm V_{\rm CC}$      |

| A12           | A12   | $A12 \square 2$        | 6264   | 9 - 98 _ 3                  | VE WE               | WE                    |

| A7            | A7    | $A7 \qquad \boxed{3}$  |        |                             | S1 A13              | A13                   |

| A6            | A6    | $A_6 \square 4$        | 62128  | L                           | .8 A8               | AI3                   |

| A5            | A5    | $A_5 \square 5$        |        | ''                          | .9 A9               | A9                    |

| A4            | A4    | $A_4 \qquad \boxed{6}$ | 64256  |                             | .11 A11             | A11                   |

|               |       | 444                    | 64256  |                             | DE OE               | OE                    |

| A3            | A3    | A3                     |        | F                           |                     |                       |

| A2            | A2    | A2 🗌 8                 |        | 21   A                      | .10 A10             | A10                   |

| A1            | A1    | A1 🗌 9                 | SRAM   | $_{20}$ $\square$ $\bar{c}$ | CE CE               | $\overline{	ext{CE}}$ |

| A0            | A0    | A0 🔲 10                |        | 19 🗆 D                      | 07 D7               | <b>D</b> 7            |

| $\mathbf{D0}$ | D0    | D0 🖂 11                |        |                             | 06 D6               | D6                    |

| D1            | D1    | D1 🖂 12                |        | 18 🗖 D                      | 05 D5               | D5                    |

| D2            | D2    | D2 🔲 13                |        | 17 🗀 D                      | 04 D4               | D4                    |

| GND           | GND   | GND ☐ 14               |        | 16 🗆 D                      | 03 D3               | D3                    |

|               |       |                        |        |                             |                     |                       |

## 7.3.1 常用数据存储器芯片

6116/6264/62128/62258的操作方式

| 方式。                 | I脚→<br>CE → | <u>OE</u>        | ₩E↔                  | DO~D7₽ | 4  |

|---------------------|-------------|------------------|----------------------|--------|----|

| ·<br>读 <sub>4</sub> | 0₽          | 0.               | 10                   | Dout₽  | 4  |

| 写↩                  | 0.          | 14               | 0₽                   | Din₽   | ₽  |

| 维 持*↵               | 1.0         | X <sub>4</sub> 3 | $\mathbf{X}_{e^{2}}$ | 高阻₽    | ته |

#### 注: X代表任意状态。

\*代表对于CMOS静态RAM电路,CE为高电平时,电路处于降耗状态。此时V<sub>cc</sub>可降至3V左右,内部所存数据也不会丢失。

## 7.3.2 数据存储器扩展实例

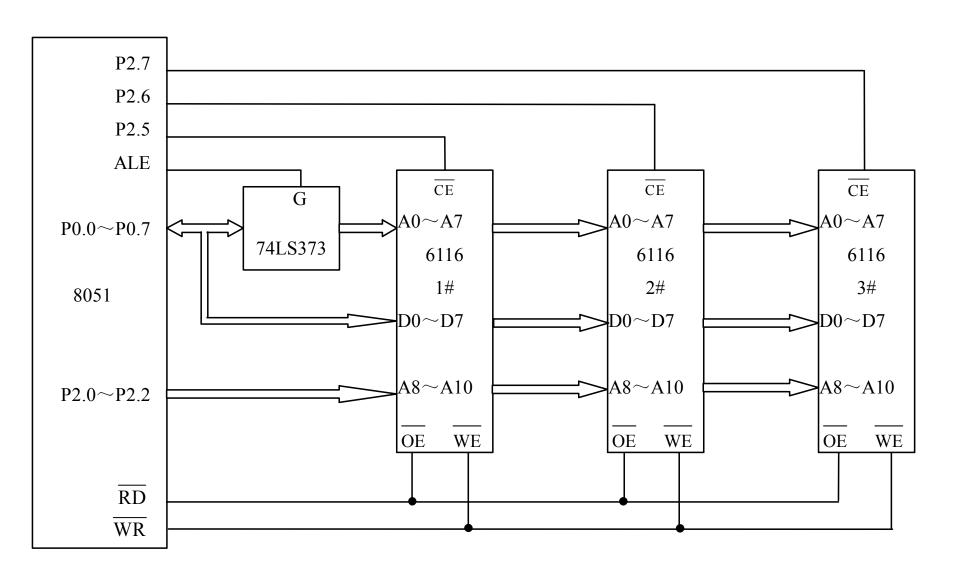

【例3】 8051扩展三片6116静态RAM(6KB)。

解:扩展静态RAM与扩展ROM相似,只是控制信号有所不同,如下图所示为8051用线选法扩展2KB静态RAM6116的连线图。

单片机的RD接EPROM的输出允许OE; WR接EPROM的写允许WE。

P2口的P2.3、P2.4未用,所以它们的状态与2764的寻址无关;假设无关位P2.3和P2.4为0,则1号片的地址为C000H~C7FFH,2号片的地址为A000H~A7FFH,3号片的地址为6000H~67FFH。

#### 8051扩展6KB RAM

## 7.3.2 数据存储器扩展实例

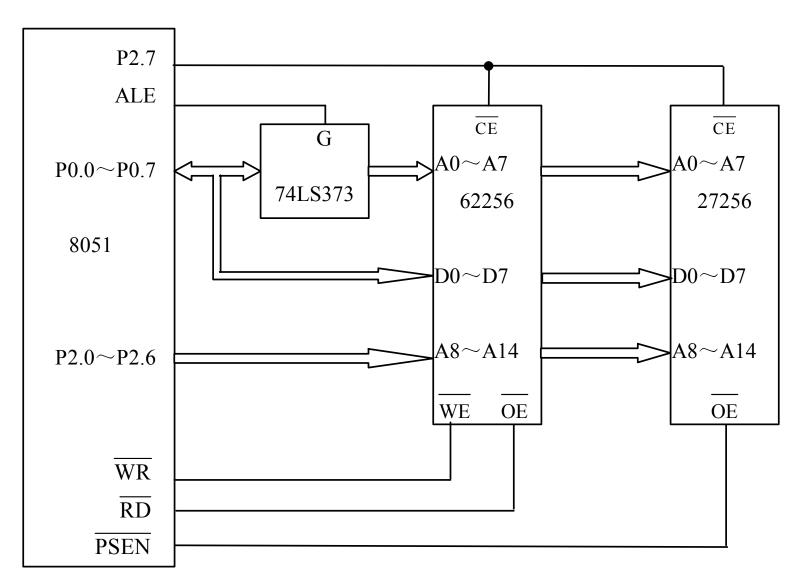

【例4】8051同时扩展一片62256 RAM和一片27256 ROM。解:用线选法同时扩展一片62256 RAM和一片27256 ROM,逻辑电路图如下图所示。

32KB EPROM的地址为 0000H~7FFFH,

32KB RAM的地址也为 0000H~7FFFH;

虽然片选信号同为P2.7,两者的地址相同,但不会发生地址冲突;因为外部RAM的读写控制信号为RD和WR,它们由MOVX指令产生,而外部ROM的读控制信号在CPU向外部ROM取指令时才产生,也就是说外部RAM的读写控制信号与外部ROM的读控制信号不会同时产生。

#### 8051扩展ROM与RAM的逻辑电路图

# 7.4 简单并行1/0接口扩展

- 7.4.1 简单I/O接口扩展常用芯片

- 7.4.2 简单并行I/0接口扩展实例

## 7.4.1 简单I/0接口扩展常用芯片

- 简单I/O接口扩展所用芯片为74系列的TTL电路,CMOS电路也可作为MCS-51的扩展I/O接口。这些芯片结构简单,配置灵活方便,比较容易扩展,使系统降低了成本、缩小了体积,因此在单片机应用系统中经常被采用。

- · 常用芯片有74LS244(八缓冲器/线驱动器/线接收器)、74LS245(八双向总线收发器)、74LS273(八D触发器)、74LS373(八D锁存器)、74LS377(带使能的八D触发器)等。

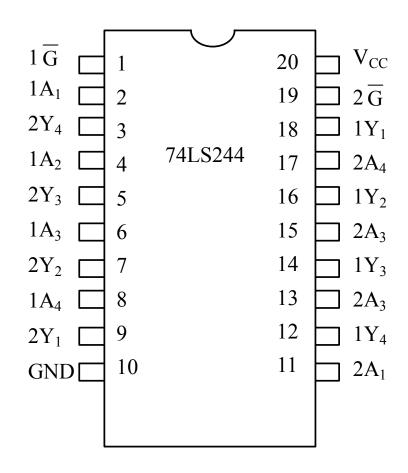

- 74LS244是八缓冲器/线驱动器/线接收器,内部有两组4 位三态缓冲器,具有数据缓冲隔离和驱动作用,其输入阻 抗较高,输出阻抗低,常用于单向三态缓冲输出。

### 7.4.1 简单I/0接口扩展常用芯片

#### 74LS244各引脚定义如下:

- 1A1~1A4:第1组4条输入线

- 1Y1~1Y4: 第1组4条输出线

- 2A1~2A4:第2组4条输入线

- 2Y1~2Y4: 第2组4条输出线

- 1G:第1组三态门使能端,

- 低电平有效

- 2**G**:第2组三态门使能端,

- 低电平有效

- V<sub>cc</sub>: 工作电源,接+5V电压

- **GND**:接地

# 7.4.1 简单I/O接口扩展常用芯片

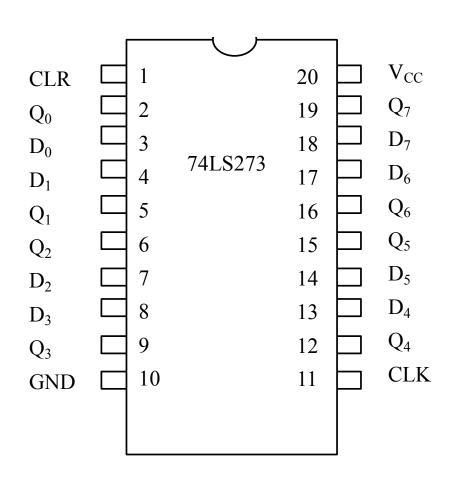

#### 74LS273各引脚定义如下:

**D0~D7:输入线。**

**■ Q0~Q7**:输出线。

CLR:清除控制端,

低电平有效。

CLK: 时钟输入端,

上升沿有效。

V<sub>cc</sub>: 工作电源,

接+5V电压。

• GND:接地。

# 7.4.1 简单1/0接口扩展常用芯片

#### 74LS244的工作方式

|                  | 输入    | 输 出₽       |                        |   |

|------------------|-------|------------|------------------------|---|

| 1 <del>G</del> ₽ | 2 G & | A₽         | $\mathbf{Y}_{\varphi}$ |   |

| 0₽               | 0.0   | <b>0</b> ¢ | 0€                     | 4 |

| 0₽               | 0.0   | 10         | 1₽                     | + |

| 1₽               | 1.₽   | X₽         | 高阻↩                    | 4 |

#### 74LS273的工作方式

| 输 入₽ |            |                      | 输 出↵ |            |  |

|------|------------|----------------------|------|------------|--|

| CLR4 | CLK₽       | $\mathbf{D}_{arphi}$ | Q₽   | 4          |  |

| 0€   | X↔         | $X_{\epsilon^j}$     | 1.0  | ē          |  |

| 10   | <b>↑</b> ₽ | 0.€                  | 0€   | 4          |  |

| 1€   | <b>↑</b> ₽ | 1.0                  | 1₽   | ت <u>ـ</u> |  |

| 1₽   | 0.₽        | $X_{\phi}$           | 锁存₽  | 43         |  |

# 7.4.2 简单并行1/0接口扩展实例

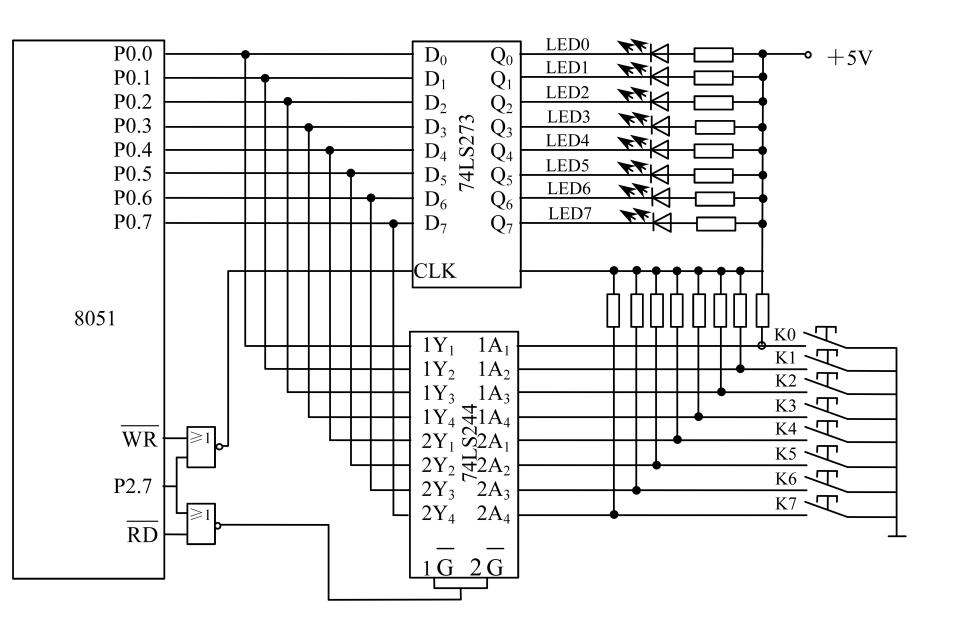

【例5】用74LS244作为扩展输入,74LS273作为扩展输出。

解: P0口作为双向数据总线,用74LS244扩展8位输入,输入 八只控制开关的控制信号;用74LS273扩展8位输出,输 出信号控制八只发光二极管。编写控制程序,可使八只发光 二极管分别受各自对应的控制开关的控制。

只要P2.7为0,就选中74LS244或74LS273,其他位均为无 关位,所以74LS244和74LS273的地址均为7FFFH。

#### 简单I/O口扩展电路

### 参考程序:

|       |    |    |    |       | ORG 0000H       |         |

|-------|----|----|----|-------|-----------------|---------|

| 0000н | 01 | 50 |    |       | AJMP MAIN       |         |

|       |    |    |    |       | ORG 0050H       |         |

| 0050н | 90 | 80 | 00 | MAIN: | MOV DPTR, #8000 | ;置输入口地址 |

| 0053н | ΕO |    |    |       | MOVX A,@DPTR    | ;读输入口数据 |

| 0054н | 90 | 90 | 00 |       | MOV DPTR,#9000H | ;置输出口地址 |

| 0057н | FO |    |    |       | MOVX @DPTR,A    | ;写输出口数据 |

| 0058н | 80 | F6 |    |       | SJMP MAIN       |         |

|       |    |    |    |       | END             |         |

# 7.5 8255可编程并行接口扩展

- 7.5.1 8255A的结构

- 7.5.2 8255A的工作方式

- 7.5.3 8255A可编程并行接口扩展应用实例

- 8255A是一个可编程并行接口芯片,它主要作为外围设备 与微型计算机总线之间的I/O接口。

- 8255A可以通过软件来设置芯片的工作方式,因此用 8255A连接外部设备时,通常不需要再附加外部电路,给 使用带来很大的方便。

- 8255A有三个8位可编程并行I/O端口,从编程上可分成2组, 每组12个,有3种工作模式。

### 8255A各引脚定义如下:

- $D_7 \sim D_0$ : 双向数据线,用于传送数据和控制字。

- PA<sub>7</sub>~PA<sub>0</sub>、PB<sub>7</sub>~PB<sub>0</sub>、PC<sub>7</sub>~PC<sub>0</sub>: 输入/输出信号线,用于传送数据。

- CS: 片选信号,低电平有效。只有该引脚为低电平时, 8255A才与CPU建立通信。

- RD: 芯片读出信号,低电平有效。当引脚为低电平时,CPU 可以从8255A中读取输入数据。

- WR: 芯片写入信号,低电平有效。当引脚为低电平时,CPU 可以往8255A中写入数据或控制字。

### 8255A各引脚定义如下:

A<sub>0</sub>、A<sub>1</sub>:端口选择信号,这两个引脚的输入和RD、WR两个引脚的输入,一起控制8255A内部三个数据端口及一个控制端口的选择。它们一般和地址总线的两个最低位(A<sub>0</sub>、A<sub>1</sub>)相连。选择如下:

A1A0为00时选中端口A;为01时选中端口B;为10时选中端口C;为11时选中命令字口。

RESET:复位,当该输入信号为高电平时,控制寄存器被清除,所有的端口(A、B、C)都被设为输入状态。复位引脚上的高电平,使各个端口都置为输入模式(也就是24个引脚都被置为高阻态)。

### 8255A的引脚与封装

|                        |               | _ |    |            |    | ¬                                  |

|------------------------|---------------|---|----|------------|----|------------------------------------|

| $PA_3$                 | <b>*</b>      |   | 1  | $\bigcirc$ | 40 | $\rightarrow$ PA <sub>4</sub>      |

| $PA_2$                 | <b>↔</b>      |   | 2  |            | 39 | $\rightarrow$ PA <sub>5</sub>      |

| $PA_1$                 | <b>*</b>      |   | 3  |            | 38 | $\rightarrow$ PA <sub>6</sub>      |

| $PA_0$                 | <b>*</b>      |   | 4  |            | 37 | $\rightarrow$ PA <sub>7</sub>      |

| $\overline{\text{RD}}$ | $\rightarrow$ |   | 5  |            | 36 | $\square \leftarrow \overline{WR}$ |

| $\overline{\text{CS}}$ | $\rightarrow$ |   | 6  |            | 35 | ☐ ← RESE                           |

| Vss                    |               |   | 7  |            | 34 | $\longrightarrow$ D <sub>0</sub>   |

| $A_1$                  | $\rightarrow$ |   | 8  |            | 33 | $\longrightarrow$ D <sub>1</sub>   |

| $A_0$                  | $\rightarrow$ |   | 9  |            | 32 | $\square \iff D_2$                 |

| $PC_7$                 | <b>*</b>      |   | 10 | _          | 31 | $\square \iff D_3$                 |

| $PC_6$                 | <b>*</b>      |   | 11 | 8255A      | 30 | $\square \iff D_4$                 |

| $PC_5$                 | <b>*</b>      |   | 12 | 82         | 29 | $\longrightarrow$ D <sub>5</sub>   |

| $PC_4$                 | <b>*</b>      |   | 13 |            | 28 | $\longrightarrow$ D <sub>6</sub>   |

| $PC_0$                 | <b>*</b>      |   | 14 |            | 27 | $\longrightarrow$ D <sub>7</sub>   |

| $PC_1$                 | <b>*</b>      |   | 15 |            | 26 | $\square$ $V_{CC}$                 |

| $PC_2$                 | <b>*</b>      |   | 16 |            | 25 | $\square \iff PB_7$                |

| $PC_3$                 | <b>*</b>      |   | 17 |            | 24 | ightharpoonup PB <sub>6</sub>      |

| $PB_0$                 | <b>*</b>      |   | 18 |            | 23 | $\square \iff PB_5$                |

| $PB_1$                 | <b>*</b>      |   | 19 |            | 22 | ightharpoonup PB <sub>4</sub>      |

| $PB_2$                 | <b>*</b>      |   | 20 |            | 21 | $\square \iff PB_3$                |

|                        |               |   |    |            |    | 1                                  |

| 数据线  |

|------|

| 复位输入 |

| 芯片使能 |

| 读    |

| 写    |

| 端口地址 |

| 端口 A |

| 端口 B |

| 端口 C |

| 电源   |

| 地    |

|      |

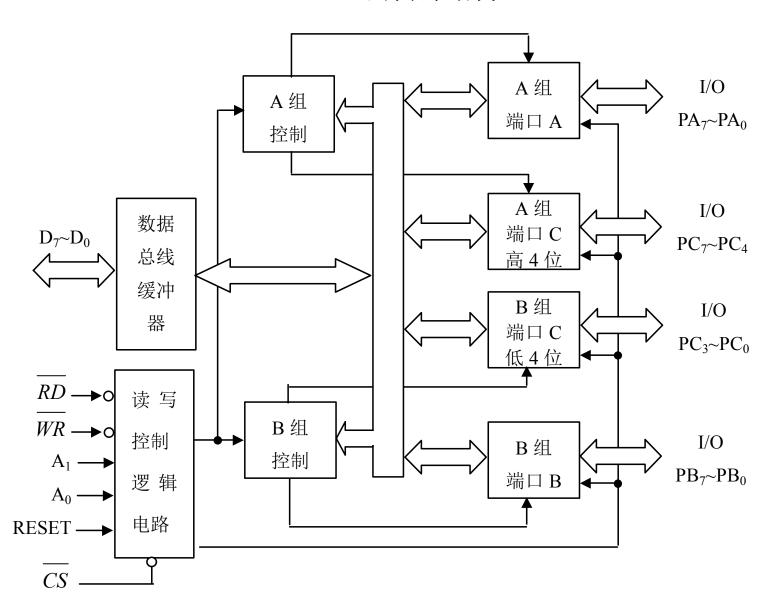

#### 8255A的内部结构

### 8255A可编程接口的组成

### 数据总线缓冲器

这是一个双向三态的8位数据缓冲器,8255A正是通过它和系统数据总线相连。该缓冲器根据CPU的输入或输出指示来传递或接收数据。CPU发给8255A的控制字和状态字也是通过这个缓冲器传递的。

### • 读/写控制逻辑电路

这部分电路管理所有数据、控制信息、状态信息的内部及外部的传递。它接收来自CPU地址总线和控制总线的信号,据此向控制部件提出请求。

### 8255A可编程接口组成

### **A**组控制和B组控制

每个端口的功能配置都是由系统软件来实现的。实质上也就是CPU给8255A一个控制字。控制字中含有"工作方式"、"按位置位"、"按位复位"等一些信息,依此来初始化8255A的功能配置。每个控制块(A组控制和B组控制)一方面接收来自读/写控制逻辑电路的"请求"信号,一方面接收来自内部数据总线的"控制字",并据此决定相连端口的合适工作方式。但控制字寄存器只能写,不能读。控制字可分为两类,一类为各端口的方式选择控制字;一类为端口C按位置位/复位的控制字。

A组控制:控制端口A和端口C的高位( $PC_7 \sim PC_4$ )

B组控制:控制端口B和端口C的低位( $PC_3 \sim PC_0$ )

### 8255A可编程接口组成

- 端口A、B、C

- 8255A有三个8位数据端口(A、B、C)。设计人员可以用软件使它们分别作为输入端口或输出端口。不过,这3个端口有着各自的特点以增强8255A的能动性和弹性。

- 端口A:对应一个8位数据输出的锁存器/缓冲器和一个8位数据输入的锁存器。

- » 端口B:对应一个8位数据输入\输出的锁存器/缓冲器和一个8位数据输入的缓冲器。

### 8255A可编程接口组成

- 端口A、B、C

- 端口C:对应一个8位数据的输出锁存器/缓存器和一个8位数据的输入缓存(对于输入没有锁存)。该端口可以在8255A的不同工作方式下被分成2个4位端口,每个4位端口都包括一个4位的锁存,并为端口A和端口B提供控制信号输出和状态信号输入。

8255A可编程接口主要由以下几部分组成:

- 端口A、B、C

- 端口A、B的工作方式可以分别定义,而端口C要依据A、B的工作方式来分成两部分。所有的输出寄存器,包括状态锁存器(Status Flip-Flops),在任何模式转换时都会被复位。各个工作方式可以相结合,因此对于所有的I/O结构来说,它们的功能都可以被裁剪。

例如:端口B可以设置为方式0,监视简单的开关结束,或者显示计算的结果,而端口A可以在方式1下工作,检测键盘的输入,或者检测一个靠基本中断工作的磁带播放机的播放。

- · 8255A在三种基本的方式下工作:

- 方式 0: 基本输入/输出。

- 方式 1: 选通的输入/输出。

- 方式 2: 双向传输。

### 1. 方式0(基本输入/输出)

这种工作方式是指三个数据端口提供简单的输入和输出功能。不需要"握手"信号,数据仅是简单地写进特定的端口,或从该端口读出。

### 方式0的基本工作特点如下:

- 两个八位的端口和两个4位的端口。

- 任何端口都可以输入或者输出。

- 输出被锁存。

- 输入不被锁存。

- 在该方式下,各端口的输入/输出有16种不同的组合。

### 2. 方式1(选通的输入/输出)

这种工作方式要依据选通信号或者"握手"信号来进行数据的传递。在该方式下,端口A、B要利用端口C来产生或接收"握手"信号。

### 方式1的基本工作特点如下:

- 端口A、B都可单独在方式1下作输入端口或输出端口,以支持各种选通的I/0应用程序。

- 每组包括一个8位的数据端口和一个4位的控制/数据端口。

- 4位的端口要为8位的数据端口提供控制和状态信息。

#### 2. 方式1(选通的输入/输出)

输入的控制信号功能如下:

- STB(选通信号输入端):该引脚为低电平时,数据被送入输入锁存器。

- IBF(输入缓冲器满信号):8255A的输出状态信号,高电平有效,表明输入缓冲器已满,即已有一个新数据写入缓存器。IBF信号是由STB信号使其置位的,而由读信号RD的上升沿复位。

- INTR(中断请求): 当某个输入装置需要服务时,该信号为高电平,向 CPU提出中断请求。当STB、IBF以及INTE(中断允许标志)均为高电平时, INTR将被置为高电平;由读信号RD的下降沿使其复位。这个程序使得 输入设备仅通过选通信号就可向CPU提出中断,要求其给予服务。

#### 2. 方式1(选通的输入/输出)

输出控制信号功能如下:

- OBF(输出缓存满信号):低电平有效,由8255A送给外设。有效时表明 CPU已经向指定的端口输出了数据。由输入信号WR的上升沿使OBF置位, 由输入信号ACK的有效信号使其复位。

- ACK(外设响应输入):该输入信号的低电平通知8255A端口A或端口B的数据已被接收,从本质上来说该信号是来自外围设备的响应信号,表明外围设备已经接收来自CPU的数据。

- INTR(中断请求): 当一输出设备已接收来自CPU的数据时,该信号为高电平,用来向CPU提出中断请求。当ACK、OBF以及INTE均为高电平时,该信号被置为高电平;写信号WR的下降沿使其复位。

- INTE A(A口中断允许标志)由按位置位/复位的PC<sub>6</sub>控制; INTE B(B口中断允许标志)由PC<sub>2</sub>控制。

#### 3. 方式2(选通的双向总线输入/输出)

这种工作方式方便了8255A和外围设备或外围系统之间在一个8位总线上的通信(双向输入\输出总线)。"握手"信号用来维持适当的总线流动规则,使该方式与方式1有相似的风格。中断产生机制和允许/不允许机制也适用于方式。

#### 方式2的基本工作特点如下:

- 只适用于端口A。

- 一个8位的双向总线端口(端口A)和一个5位的控制端口(端口C)。

- 输入和输出数据都被锁存。

- 端口C的5个数位为8位的双向总线端口A提供控制和状态信息。

- 双向输入/输出总线的控制信号——INTR(中断请求),这是一个高电平 有效的输出信号,是8255A发给CPU要求其写入或接收数据的中断请求。

### 3. 方式2(选通的双向总线输入/输出)

输出的控制信号功能如下:

- OBF(输出缓冲满): 该输出信号低电平有效,表明CPU已往 端口写入数据。

- ACK (响应信号): 该输入信号低电平有效,有效时使得端口A的三态输出缓冲器输出数据,反之,输出缓冲器将处于高阻态。

- INTE1(和OBF相连的双稳态多谐振荡器的INTE信号):由按 位置位/复位的PC6控制。

### 3. 方式2(选通的双向总线输入/输出)

输入的控制信号功能如下:

- STB(选通输入):该输入信号低电平有效,有效时将外设传来的数据输入锁存器。

- IBF(输入缓存满): 该输出信号高电平有效,表明数据已被输入锁存器。

- INTE2(和IBF相连的双稳态多谐振荡器的INTE信号):由按 位置位/复位的PC4控制。

### 4. 端口C按位置位/复位的特点

- 端口C的任一位都可由一个输出指令置位或者复位。这个特点也减少了基于控制的应用软件中的软件请求。当端口C用来为端口A、B提供状态/控制信号时,C的每一位都可由按位置位/复位操作来置位或复位,看起来就像是数据输出端口。

- 8255A工作在方式1或方式2下时,控制信号也就是8255A发给CPU的中断请求。中断请求信号一般是由端口C发出的,由相连的INTE(中断允许)双稳态多谐振荡器用端口C的按位置位/复位功能来禁止或允许。这种方式允许编程人员控制特定的I/O设备向CPU发出的中断信号,同时不会影响中断体系中的其他设备。

### 5. 方式控制字

方式选择控制字的格式如下:

$D_7 D_6 D_5 D_4 D_3 D_2 D_1 D_0$

- D<sub>7</sub>: 1.

- D<sub>6</sub>D<sub>5</sub>:端口A工作方式选择。00代表方式0;01代表方式1; 1x代表方式2。

- D<sub>4</sub>:端口A的输入/输出选择。1代表输入;0代表输出。

- $D_3$ :  $PC_7 \sim PC_4$ 的输入/输出选择。1代表输入;0代表输出。

- D<sub>2</sub>:端口B工作方式选择。0代表方式0;1代表方式1。

- $D_1$ : 端口B的输入/输出选择。1代表输入;0代表输出。

- D<sub>0</sub>: PC<sub>3</sub>~PC<sub>0</sub>的输入/输出选择。1代表输入;0代表输出。

### 5. 方式控制字

端口C按位置位/复位的控制字的格式如下:

$$D_7 D_6 D_5 D_4 D_3 D_2 D_1 D_0$$

- $D_7: 0$  •

- D<sub>6</sub>D<sub>5</sub>D<sub>4</sub>: 无关。

- D₃D₂D₁:端口C的位选择:

000代表PC<sub>0</sub>; 001代表PC<sub>1</sub>; 010代表PC<sub>2</sub>; 011代表PC<sub>3</sub>。

100代表PC4; 101代表PC5; 110代表PC6; 111代表PC7。

D₀: 1代表置1; 0代表置0。

- 7.5.3 8255A可编程并行接口扩展应用实例

- 【例6】用8255的PA、PB、PC口分别作为输入口接八只控制 开关,或作为输出口接八只发光二极管,编写控制程序, 使八只发光二极管分别受各自对应的控制开关的控制。

- 解:假设:端口A地址为FF28H,端口B地址为FF29H,端口C地址为FF2AH,控制端口地址为FF2BH。PA口作为输入口接八只控制开关,PB口作为输出口接八只发光二极管。

### 7.5.3 8255A可编程并行接口扩展应用实例

#### 参考程序:

| 地址    |    | 机器 | 器码 |       |      | 程序           | 注释         |

|-------|----|----|----|-------|------|--------------|------------|

|       |    |    |    |       | ORG  | 0000н        |            |

| 0000н | 41 | 50 |    |       | AJMP | MAIN         |            |

|       |    |    |    |       | ORG  | 0250Н        |            |

| 0250Н | 90 | FF | 2B | MAIN: | MOV  | DPTR,#0FF2BH |            |

| 0253Н | 74 | 90 |    |       | MOV  | А,#90Н       | ;A口输入、B口输出 |

| 0255Н | F0 |    |    |       | MOVX | @DPTR,A      | ;写控制字数据    |

| 0256Н | 90 | FF | 28 | LOOP: | MOV  | DPTR,#0FF28H |            |

| 0259Н | EO |    |    |       | MOVX | A,@DPTR      | ;读输入口数据    |

| 025AH | 90 | FF | 29 |       | MOV  | DPTR,#0FF29H |            |

| 025DH | F0 |    |    |       | MOVX | @DPTR,A      | ;写输出口数据    |

| 025EH | 80 | F6 |    |       | SJMP | LOOP         |            |

|       |    |    |    |       | END  |              | ;程序结束      |

### 7.5.3 8255A可编程并行接口扩展应用实例

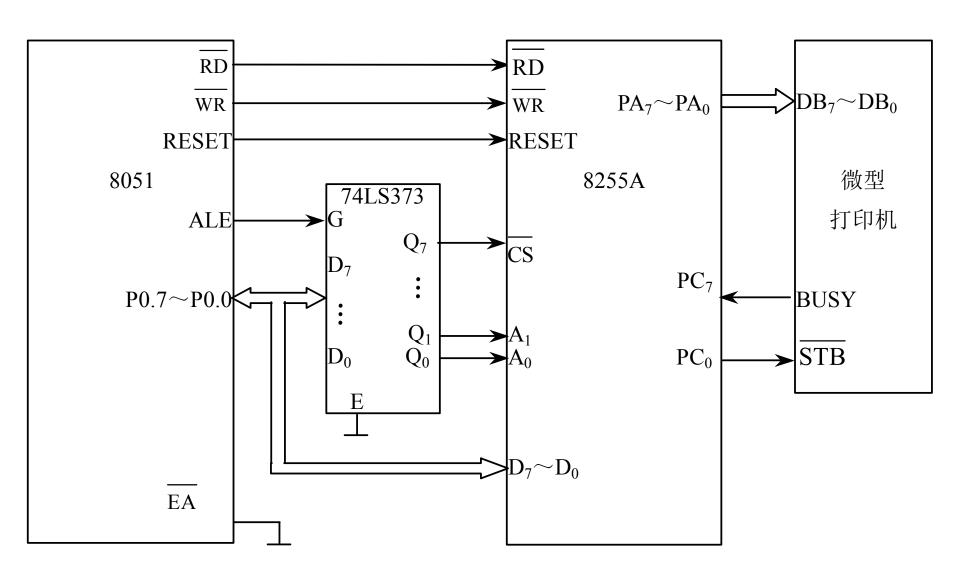

【例7】 用8255控制打印机,打印机与8051采用查询方式交换数据。

解:下图是8255A作为打印机接口与8051相连的电路图。其工作方式为0,片选信号为P0.7,端口A作数据输出通道,端口B不用,PC7与打印机的状态信号BUSY相连,PC0与打印机的选通信号STB。打印机与8051采用查询方式交换数据。当BUSY为0,在STB负跳变时,数据被输入。

按照接口电路可知(无关的位全设为1),端口A地址为7CH,端口B地址为7DH,端口C地址为7EH,控制端口地址为7FH。方式选择字(无关的位全设为0)为88H。要打印的数据开始地址为30H;要打印的数据个数设为50。

#### 8051通过8255A与打印机电路图

#### 参考程序:

START: MOV R5, #32H ; 要打印的数据个数放在R5中

MOV

R6, #30H

; R6指向数据开始地址

MOV

R0, #7FH

; 方式选择控制字地址

MOV A, #88H ; 使端口A工作于方式0, 且为输出C的高位为输入, 低位为

输出

MOVX @ RO. A

MOV RO, #7FH

MOV A, #71H ; 用按位置位/复位的方法, 使PCO为1, 即使STB为高电平

MOVX @ RO, A

LP: MOV RO, #7EH ; 读端口C的值

MOVX A, @RO

ANL A, #80H ; 求与, 查看PC7, 即状态信号BUSY的值

JNZ LP ; 若不为0, 说明打印机现在处于忙状态, 跳转继续读端口C

的值

MOVX A. @R6 : 若不忙,将要打印的字符送往端口A

MOV RO, #7CH

MOVX @RO, A

MOV RO, #7FH

MOV A, #70H ; 同上, 使STB变为低电平

MOVX @ RO, A

INC R6 ; 指向下一个要打印的数据

MOV RO, #7FH ; 再使STB为1

MOV A, #71H

MOVX @ RO, A

DJNZ R5. LP : 将要打印的个数减1. 并判断是否打印完. 否则跳转

**END**

# 7.6 8155可编程并行接口扩展

- 7.6.1 8155的结构

- 7.6.2 8155的工作方式

- 7.6.3 8155可编程并行接口扩展应用实例

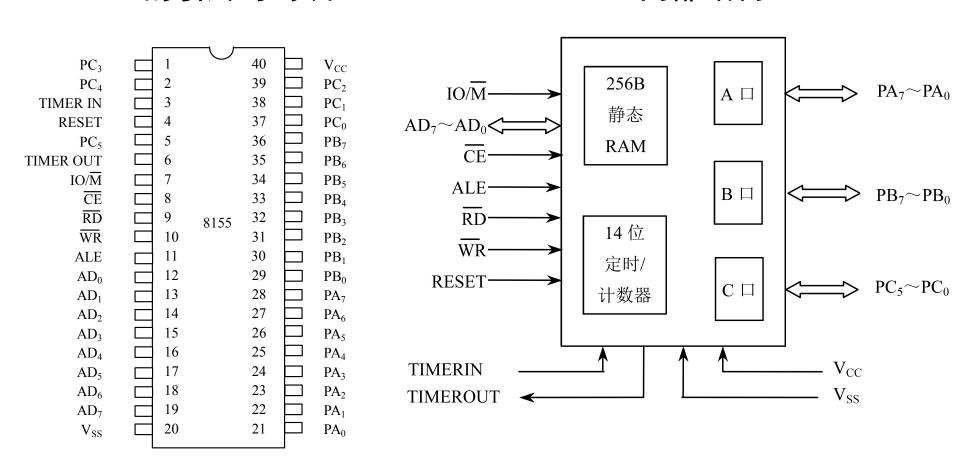

- 8155是一种多功能可编程外围扩展接口芯片,它也有三个可编程I/0端口(端口A、B、C)。

- 与8255A的区别在于PC口是6位,同时还有一个可编程14位 定时器/计数器和256字节的RAM,能方便地进行I/O扩展和 RAM扩展。

#### 8155各引脚定义如下:

- AD<sub>0</sub>~AD<sub>7</sub>: 三态地址/数据复用线。因8155片内有地址锁存器,该组引脚直接与单片机的P0口相连。

- $PA_0 \sim PA_7$ 、 $PB_0 \sim PB_7$ : 端口A和端口B用于传送数据。

- $PC_0 \sim PC_5$ : 端口C既可用于传送数据,也可用作端口A和端口B的控制信号线。

- RESET:复位输入信号,高电平有效。

- CE: 片选信号,低电平有效。

- RD: 读选通信号,低电平有效。

- WR: 写选通信号, 低电平有效。

- IO/M: RAM及I/O选择。在片选信号有效的情况下,该信号为高电平,表明单片机选择的是8155的I/O读写;为低电平,表明单片机选择的是8155的RAM读写。

- ALE: 地址锁存信号。8155片内有地址锁存器,该信号的下降沿将 AD<sub>0</sub>~AD<sub>7</sub>上的地址信息以及CE、IO/M的状态锁存在8155的内部寄存器 内。

- TIMERIN: 定时/计数器的输入端

- TIMEROUT: 定时/计数器的输出端

#### 8155的引脚与封装

#### 8155内部结构

#### 8155内部的I/O口、RAM、定时器和命令/状态寄存器的地址分配

| $A_7$ | $A_6$ | $A_5$ | $A_4$ | $A_3$ | $A_2$ | $A_1$ | $A_0$ | 选中寄存器    |

|-------|-------|-------|-------|-------|-------|-------|-------|----------|

| ×     | ×     | ×     | ×     | ×     | 0     | 0     | 0     | 命令/状态寄存器 |

| ×     | ×     | ×     | ×     | ×     | 0     | 0     | 1     | РАП      |

| ×     | ×     | ×     | ×     | ×     | 0     | 1     | 0     | РВ□      |

| ×     | ×     | ×     | ×     | ×     | 0     | 1     | 1     | РСП      |

| ×     | ×     | ×     | ×     | ×     | 1     | 0     | 0     | 定时器高8位   |

| ×     | ×     | ×     | ×     | ×     | 1     | 0     | 1     | 定时器低8位   |

## 7.6.2 8155的工作方式

### 1. 8155作片外RAM(256B)

- 在片选信号CE有效的情况下,IO/M信号为高电平,8155作 片外RAM使用。

- 地址的高8位由片选信号确定,地址的低8位为00H~FFH。

#### 2. 8155作1/0口

8155有两种工作方式:基本1/0和选通1/0。

- 当8155的PA口、PB口、PC口工作在基本I/0方式下,可用于无条件I/0 操作。基本输入时执行"MOVX A,@DPTR"类指令,基本输出时执 行"MOVX @DPTR,A"类指令。

- 当8155的PA口工作在选通I/0方式下时,PC口低三位作PA口联络线, 其余位作I/0线,PB口定义为基本I/0;PA口和PB口也可同时定义为选 通I/0,此时PC作PA口、PB口联络线。

- 在8155操作前,须由CPU向命令寄存器送命令字,设定其工作方式, 命令字只能写入不能读出。

- 8155内部还有一个状态寄存器,可以锁存8155 I/O口和定时器的当前状态,供CPU查询,状态寄存器和命令寄存器共用一个地址,只能读出不能写入。因此可以认为8155的00H口是命令/状态口,CPU往00H写入的是命令字,而从中读出的是状态字。

#### 2. 8155作1/0口

8155命令寄存器格式如下表所示。

| $\mathbf{D}_7$ | D <sub>6</sub> | $D_5$ | $\mathbf{D_4}$ | $D_3$           | $\mathbf{D_2}$  | $\mathbf{D}_1$ | $D_0$ |

|----------------|----------------|-------|----------------|-----------------|-----------------|----------------|-------|

| TM2            | TM1            | IEB   | IEA            | PC <sub>2</sub> | PC <sub>1</sub> | PB             | PA    |

#### 各位功能说明如下:

- TM2 TM1:

- 》 00 代表空操作。

- 01 代表停止计时。

- 10 代表时间到则停止计时。

- 11 代表置入定时器方式控制字和计数初值后,立即启动计时。若正在 计时,溢出后按新的定时器方式和计数初值计时。

#### 2. 8155作1/0口

- IEB: 0代表禁止PB口中断; 1代表允许PB口中断。

- IEA: 0代表禁止PA口中断; 1代表允许PA口中断。

- $PC_2 PC_1$ :

- DO 代表PA、PB均为基本I/O方式,PA和PB输入/输出由D₁D₀确定,PC口输入。

- > 01 代表PA、PB均为基本I/O方式,PA和PB输入/输出由D1DO确定,PC口输出。

- 10 代表PA选通I/0,PB为基本I/0方式,输入\输出由D1D0确定,PC<sub>0</sub>~PC<sub>2</sub>为PA口联络线,PC3~PC5输出。

- $\sim$  11 代表PA、PB均为选通方式,输入\输出由D1D0确定,PC<sub>0</sub>~PC<sub>2</sub>为PA口联络线,PC<sub>3</sub>~PC<sub>5</sub>为PB口联络线。

- PB:0代表输入;1代表输出

- PA: 0代表输入;1代表输出

#### 2. 8155作1/0口

8155状态寄存器格式如下表所示。

| $\mathbf{D}_7$ | $\mathbf{D}_6$                 | $\mathbf{D}_5$                | $\mathbf{D}_4$                   | $\mathbf{D}_3$               | $\mathbf{D}_2$              | $\mathbf{D}_1$                   | $\mathbf{D}_0$               |

|----------------|--------------------------------|-------------------------------|----------------------------------|------------------------------|-----------------------------|----------------------------------|------------------------------|

| ×              | TIMER                          | INTEB                         | BEF                              | INTRB                        | INTEA                       | ABF                              | INTRA                        |

| 未用             | 定时中断  1: 计数 器溢出标志  0: 读出 状态或复位 | B口中断<br>允许位<br>1: 允许<br>0: 禁止 | B口缓<br>冲器满标<br>志<br>0: 空<br>1: 满 | B口中断<br>请求标志<br>0: 空<br>1: 无 | A口中断<br>允许位<br>0:禁止<br>1:允许 | A口缓<br>冲器满标<br>志<br>0: 空<br>1: 满 | A口中断<br>请求标志<br>0: 无<br>1: 有 |

#### 3. 8155作定时器

8155的可编程14位定时器/计数器是一个减法计数器,定时或计数的脉冲来自外部,它由两个8位寄存器组成。

8155定时器/计数器格式如下表所示。

|     | $\mathbf{D}_7$ | $\mathbf{D}_6$ | $\mathbf{D}_5$  | $\mathbf{D_4}$  | $D_3$           | $\mathbf{D_2}$  | $\mathbf{D}_1$ | $\mathbf{D_0}$ |

|-----|----------------|----------------|-----------------|-----------------|-----------------|-----------------|----------------|----------------|

| 高8位 | M <sub>2</sub> | M <sub>1</sub> | T <sub>13</sub> | T <sub>12</sub> | T <sub>11</sub> | T <sub>10</sub> | T <sub>9</sub> | T <sub>8</sub> |

| 低8位 | $T_7$          | T <sub>6</sub> | $T_5$           | $T_4$           | $T_3$           | $T_2$           | $T_1$          | $T_0$          |

#### 各位功能说明如下:

- M<sub>2</sub>M<sub>1</sub>:输出方式。8155定时器的输出方式与输出波形如下表所示。

- $T_{13} \sim T_0$ : 14位计数初值

### 3. 8155作定时器

8155定时器的输出方式与输出波形如下表所示。

| $M_2 M_1$ | 方 式  | 输出波形 |

|-----------|------|------|

| 0 0       | 单次方波 |      |

| 0 1       | 连续方波 |      |

| 1 0       | 单脉冲  |      |

| 1 1       | 连续脉冲 |      |

### 7.6.3 8155可编程并行接口扩展应用实例

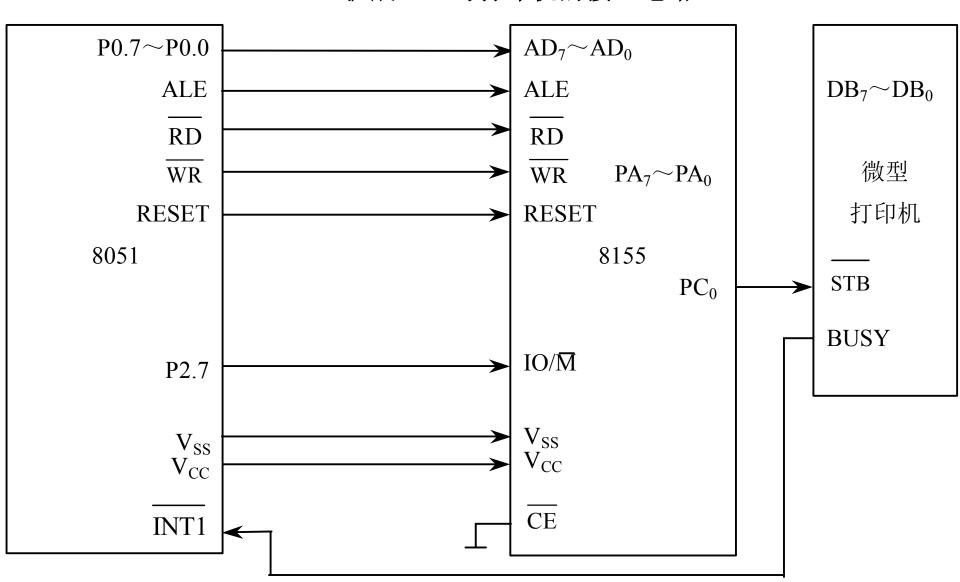

【例8】 用8155控制TPup打印机。

解: TPup打印机的接口和通用打印机相同。

下图是8051通过8155控制TPup打印机的电路图。打印机与8051采用中断方式联络。

由电路图可知:命令口地址为7FF0H,端口A地址为7FF1H,端口C地址为7FF3H,初始化命令字为0FH(端口A、端口C均输出)。

假设数据存储开始地址为20H,要打印的个数为50(32H)。

#### 8051扩展8155与打印机的接口电路

#### 参考程序:

ORG 1000H START: SETB EA : 开所有中断 EX1 :允许INT1上中断 SETB SETB PX1 :令INT1为高级中断 :令INT1为负边沿触发中断 SETB IT1 SETB P2.7 ; 令IO/M=1 R6, 20H ;要打印的开始地址放在R6中 MOV MOV R5, #32H ; R5中存要打印的数据个数,亦即中断次数 **A**, #0FH ; 方式控制字送累加器 MOV MOV DPTR. 7FF0H MOVX @DPTR, A ; 方式控制字送8155的命令端口 :第一个数据送端口A MOV A, @R6 MOV DPTR, 7FF1H MOVX @DPTR, A MOV DPTR, 7FF0H MOV A, #01H MOV @DPTR, A : PC0=1控制字送命令口 MOV A, #00H MOV @DPTR, A :PC0=0控制字送命令口 : 等待中断 LOOP: SJMP \$

#### 参考程序:

```

ORG 0003H

LJMP PINTO

ORG 2000H

PINT0:

MOV DPTR, 7FF1H

INC R6

;指向下一个数据

MOV A, @R6

MOVX @DPTR, A

MOV DPTR, 7FF3H

;产生负选通脉冲

MOV A, #01H

MOVX @DPTR, A

MOV A, #00H

MOVX @DPTR, A

;若未打完,则跳转到NEXT

DJNZ R5, NEXT

; 若打完,关中断

CLR EX1

SJMP DONE

SETB EX1

; 开中断

NEXT:

:中断返回

DONE:

RETI

END

```

### 本章小结

- 并行扩展方式一般采用总线并行扩展,即数据传送由数据 总线完成,地址总线负责外围设备的寻址,而控制总线来 完成传输过程中的传输控制。

- 在并行总线扩展中,主要介绍了两种寻址方式:线选法与译码法。该方式的扩展实例是数据存储器与程序存储器的扩展。单片机常采用数据存储与程序存储相互独立的哈佛结构体系,故存储器的扩展要分别考虑。通过本章的学习要学会画总线扩展电路图,对常用的程序存储器以及数据存储器的型号和特性要熟练掌握。

- 在I/0口并行扩展中,概略讲了简单I/0口并行扩展所用 TTL芯片;重点讲述了I/0口扩展时所用的Intel公司的可 编程芯片:8255A和8155。

## 本章小结

- 8255A是一个用在Intel公司的微型计算机系统中的可编程外围接口设备(PPI),与Intel的所有微处理器都兼容。它主要是作为外围设备和微型计算机总线间的I/0组成中的接口。由于8255A可以通过软件来设置芯片的工作方式,因此用8255A连接外部设备时,通常不需要再附加外部电路,给使用带来很大的方便。

- 8155是Intel的另一种多功能可编程外围扩展接口芯片,它也有三个可编程I/0端口(端口A、B、C),与8255A的区别在于PC口是6位,一个可编程14位定时/计数器和256字节的RAM,能方便地进行I/0扩展和RAM扩展,芯片采用40针双列直插式封装。对于这部分内容,要掌握芯片的引脚特性、内部结构以及工作方式的特点等。

### 习题

- 1. 简述什么是最小系统,什么是并行外围扩展以及并行扩展的优点?

- 2. 并行扩展包括哪几种方式,简单介绍各方式及其本质区别。

- 3. 描述总线扩展的两种寻址方式,并指出两者的区别。

- 4. 8255和8155分别有几种工作方式, 其特点是什么?

- 5.8051通过8255A与Centronic360字符打印机相连,8255A工作于方式1,且8051与打印机采用中断联络,画出电路图,并写出源程序。

- 6. 请编出把8155定时器用作400分频器的初始化程序。

Q & A?

Thanks!